-

Paper Information

- Previous Paper

- Paper Submission

-

Journal Information

- About This Journal

- Editorial Board

- Current Issue

- Archive

- Author Guidelines

- Contact Us

Microelectronics and Solid State Electronics

2012; 1(1): 15-20

doi: 10.5923/j.msse.20120101.03

Electronic Transport Properties of Junctionless Lateral Gate Silicon Nanowire Transistor Fabricated by Atomic Force Microscope Nanolithography

Farhad Larki 1, Sabar D. Hutagalung 2, Arash Dehzangi 1, E. B. Saion 1, Alam Abedini 1, A. Makarimi Abdullah 2, M. N. Hamidon 3, Jumiah Hassan 1

1Department of Physics, Faculty of Science, Universiti Putra Malaysia, Serdang, Selangor, 43400, Malaysia

2School of Materials and Mineral Resources Engineering, Universiti Sains Malaysia, Nibong Tebal, Penang, 14300, Malaysia,

3Department of Electrical and Electric Engineering, Faculty of Engineering, Universiti Putra Malaysia, Serdang, Selangor, 43400 , Malaysia

Correspondence to: Sabar D. Hutagalung , School of Materials and Mineral Resources Engineering, Universiti Sains Malaysia, Nibong Tebal, Penang, 14300, Malaysia,.

| Email: |  |

Copyright © 2012 Scientific & Academic Publishing. All Rights Reserved.

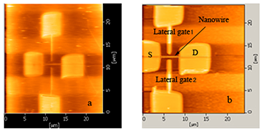

We present the fabrication, electrical characteristics, and effect of lateral gates in a junctionless silicon nanowire transistor. The transistor uses silicon nanowire on silicon-on-insulator wafer fabricated with an atomic force microscope nanolithography technique. Using AFM nanolithography allows us to make a chemical contrast between locally oxidized part of the surface and unexposed surface. This chemical contrast affects as a mask and the active part of the device is finally obtained after two step etching. The structure is uniformly low-doped for source, drain, channel, and the lateral gates regions, and confirms the behavior of junctionless nanowire transistors. The output current is controlled by channel doping and mobility of carriers instead of gate capacitance and it basically uses bulk conduction instead of surface channel conduction. The fabricated device exhibits an on-off ratio of 2×106 and a subthreshold swing of 160 mV/decade.

Keywords: Junctionless Silicon Nanowire Transistor, Lateral Gate, AFM Nanolithography, Silicon-On-Insulator (SOI)

Article Outline

1. Introduction

- During the recent years, numerous efforts have been made to do real crossing from microelectronics to nanoelectronics and to persist with scaling imposed by Moore’s law. Several technological innovations and new materials such as high κ dielectrics[1], metal gate electrodes[2], and stressors[3] have been introduced in the fabrication process. Moreover, new transistor architectures based on silicon-on-insulator (SOI), such as FinFETs[4], multi-gate FETs[5], omega-gate FETs[6], and gate-all-around FETs[7] transistors have emerged. Photolithography approaches to the limitation of its potential[8], in terms of resolution and flexibility[9]. As an alternative among the low cost routes of lithography nano-contact printing technique and atomic force microscopy (AFM) nanolithography are the promising techniques. AFM lithography and scanning tunneling microscopy (STM) lithography are belong to a group of lithography called scanning probe lithography (SPL), which is considered as one of the best lithographic technique for forming nanostructures[10]. AFM lithography holds a distinct advantage over the STM because the exposure mechanism, typically an electric field or current, can be applied independently of the feedback control of the tip-sample spacing. Moreover, fabrication using AFM lithography can be done in liquid state as well as ambient environment, whereas STM lithography is mainly carried out in ultrahigh vacuum (UHV). In addition, AFM nanolithography provides more application such as, nano manipulation[11], force lithography[12], nano grafting[13], DPL[14], and nano oxidation[15]. The principle of AFM nanolithography on SOI has been described for the first time by Snow and Campbell et al.[16-17], and they astutely expanded AFM nanolithography for fabrication of nanostructures. Ionica et al[18] have remarkably reported the electrical characteristics of the devices made by AFM nanolithography. Recently, some new works are performed to improve the method of AFM nanolithography[19-20].Fabrication of uniformly doped transistors which need no extra doping is another topic of interest and some groups already reported fabrication of structures such as accumulation metal oxide semiconductor FETs (AMOSFET)[21] and junctionless nanowire transistor (JLNWT)[22]. Fabrication of nanotransistors without junction and doping concentration was mainly considered by Shan et al[21]. Soon after that, a JLNWT was fabricated and characterized by the Tyndal group[22]. The idea behind this device is simplifying the source and drain engineering by removing the related junctions while, at the same time, sizing the silicon thickness and doping density in order to allow its switching under the gate voltage. We already reported fabrication of the single lateral gate device with low doping concentration[23]. In this work we improved the method and used the advantages of AFM nanolithography in contact mode to fabricate a nanowire transistor device with a very simple structure calling it junctionless lateral gate silicon nanowire transistor (JLGSNWT). It requires only one doping type in all regions, which is taken here to be p-type. Electrical properties of the device are described based on the junctionless transistors model and conduction mechanism of the device is compared to the conventional MOSFETs.

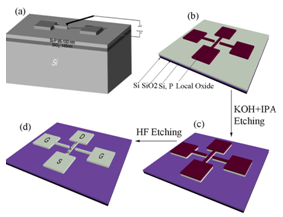

2. Fabrication Process

- The AFM nanolithography process was performed by using scanning probe microscope (SPM) machine (SPI3800N/4000). We have chosen to use the oxidation by AFM in contact mode. The main steps are schematically presented in Figure. 1 (a-d). This process was applied to a lightly doped ( 1015 cm-3) p-type (100) SOI prepared using Unibond™ process and a 145 nm buried oxide thickness [24]. The top Si layer has a thickness of 100 nm and a resistivity ρ of 13.5-22.5 Ω cm. In the fabrication process, the SOI wafer was cut into small sizes (1 cm 1 cm), cleaned by standard RCA cleaning process, and then dipped in hydrogen fluoride (HF) (1% water solution) for 30 seconds in order to replace the Si–O bonds by low energy Si–H bonds [25].

| Figure 1. Schematic of fabrication steps: (a, b) AFM local oxidation in the contact mode. (c) Wet chemical etching of the unmasked silicon. (d) Removal of the local oxide mask by etching in HF. |

3. Results and Discussion

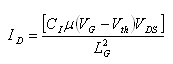

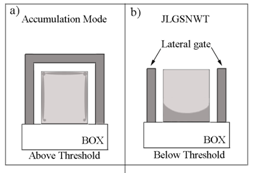

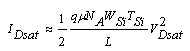

- The electrical characteristics of the junctionless lateral gate silicon nanowire FET (JLGSNWT) measured by an HP4156c semiconductor parameter analyzer (SPA, Agilent) at room temperature are shown in Figure. 3(a). The family of the characteristic curves show that the drain current (ID) decreases with the positive increase of gate voltage (VG) from 0 to +2 V. This indicates that the transistor is p-channel field effect transistor. The device has a nanowire with constant width of 95 nm, while the nanowire thickness is fixed by the silicon top layer of the SOI sample (100 nm). Electrical connections are provided by two pads which can be considered as source and drain made of same doping as silicon nanowire. The lateral gates are two wires 200 nm wide connected at one end to a contact pad and at the other end separated by 100 nm from the nanowire. It is shown that, this gap can be reduced to 30 nm without noticeable current leakage[28-29]. The characteristic curves of the device show that the drain current magnitude first increases and then saturates, which is similar to those of a conventional MOSFETs characteristics however, the fundamental of operation is completely different.

| Figure 3. I-V characteristic of the device for different lateral gate voltages VG (a), Transfer characteristics with VDS= -1 V (b). The inset shows the linear IDS vs VG plot. |

| (1) |

| Figure 4. Hole location transmission path in (a) AMOSFET and (b) JLGSNWT. |

| (2) |

| (3) |

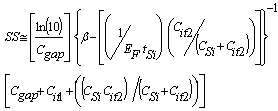

, Cgap is the capacitance of the air in the gap between channel and the gate, EF is the electric field at the Si-air interface, tSi is the thickness of top silicon layer, Cit1 is the capacitance due to the interface state density between the top silicon and the air, and Cit2 is the capacitance due to the interface state density between the top silicon and the native oxide. Since for the case of fresh sample there is no native oxide that we can consider, Cit2=0. For a top silicon thickness of 100 nm, width of 95 nm, and gate gap of 100 nm Equation (3) gives SS ≈200 mV/decade. The variance between the subthreshold swing measured from the transfer characteristic and calculated by Equation (3) can be explained by considering the effect of Si/air capacitance in the calculation. In JLNWT now it is well known that even the SiO2 capacitance has a negligible effect on the behavior of the device. The gaps between the lateral gates and the channel and the channel width reduce the effect of gates and it is the reason of high subthreshold swing of the device. Closer gates to channel distances, gates with larger cross sections, and channel with smaller cross section are critical parameters in order to achieve near ideal subthreshold swing in this structures.

, Cgap is the capacitance of the air in the gap between channel and the gate, EF is the electric field at the Si-air interface, tSi is the thickness of top silicon layer, Cit1 is the capacitance due to the interface state density between the top silicon and the air, and Cit2 is the capacitance due to the interface state density between the top silicon and the native oxide. Since for the case of fresh sample there is no native oxide that we can consider, Cit2=0. For a top silicon thickness of 100 nm, width of 95 nm, and gate gap of 100 nm Equation (3) gives SS ≈200 mV/decade. The variance between the subthreshold swing measured from the transfer characteristic and calculated by Equation (3) can be explained by considering the effect of Si/air capacitance in the calculation. In JLNWT now it is well known that even the SiO2 capacitance has a negligible effect on the behavior of the device. The gaps between the lateral gates and the channel and the channel width reduce the effect of gates and it is the reason of high subthreshold swing of the device. Closer gates to channel distances, gates with larger cross sections, and channel with smaller cross section are critical parameters in order to achieve near ideal subthreshold swing in this structures. 4. Conclusions

- We presented here the electrical characteristics of lightly doped junctionless lateral gate silicon nanowire transistors. The fabrication method used is based on AFM nanolithography on SOI substrate. The performance of device is compared to junctionless nanowire transistors. This device is a normally on device which has an off state base on depletion of the channel by electric field originated from the lateral gates. Output current of the device increases strongly with active region doping density and carriers’ mobility and it is not depends on the gate capacitance. The device uses bulk conduction instead of surface conduction. Controlling the cross section and gate gaps are key parameters for better performance of the device and particularly for subthreshold swing tuning.

ACKNOWLEDGEMENTS

- The authors gratefully acknowledge that this work was financially supported by the Science Fund from the Ministry of Science, Technology and Innovation (MOSTI), Malaysia, under project no. 03-01-05-SF0384, the USM Short Term Grant under project no. 304/PBAHAN/6039035, and UPM FRGS no. 5524051

Abstract

Abstract Reference

Reference Full-Text PDF

Full-Text PDF Full-Text HTML

Full-Text HTML