-

Paper Information

- Paper Submission

-

Journal Information

- About This Journal

- Editorial Board

- Current Issue

- Archive

- Author Guidelines

- Contact Us

Electrical and Electronic Engineering

p-ISSN: 2162-9455 e-ISSN: 2162-8459

2017; 7(3): 85-89

doi:10.5923/j.eee.20170703.03

An Optimized Performance Amplifier

Amir Ashtari Gargari, Neginsadat Tabatabaei, Ghazal Mirzaei

School of Electrical and Computer Engineering, University of Tehran, Tehran, Iran

Correspondence to: Amir Ashtari Gargari, School of Electrical and Computer Engineering, University of Tehran, Tehran, Iran.

| Email: |  |

Copyright © 2017 Scientific & Academic Publishing. All Rights Reserved.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

Amplifiers are the key components in analog or mixed-signal systems due to their domination on the system power, area, and performance parameters. Their design however, tends to become more challenging as the technology scaling continues. This work proposes an automatic design of amplifiers utilizing the induced benefits of the evolutionary algorithms. The proposed scheme is analyzed and designed on a two-stage amplifier in a 65nm process to attain the benefits of advanced CMOS technologies. An optimization technique using computational intelligence is applied to improggve the design process and the overall circuit performance. The proposed amplifier illustrates significant improvements in terms of performance, power, and area efficiency as compared with the conventional analog circuit designs.

Keywords: Computational intelligence, Automatic design, Optimization algorithm, Analog circuit design, Operational amplifier

Cite this paper: Amir Ashtari Gargari, Neginsadat Tabatabaei, Ghazal Mirzaei, An Optimized Performance Amplifier, Electrical and Electronic Engineering, Vol. 7 No. 3, 2017, pp. 85-89. doi: 10.5923/j.eee.20170703.03.

1. Introduction

- Ever growing CMOS technology scaling makes amplifier design more complicated and a key limiting factor in mixed-signal power/performance enhancement. Optimization algorithms can be a promising solution that overcomes the technical barriers in high-performance amplifier design by utilizing their capabilities of chip area, design time, and complexity reduction [1-4].Recently, some automatic circuit designs have been proposed [5, 6]. In a conventional amplifier design method, one of the major challenges is considering the desired silicon area, power/performance efficiency, and noise sensitivity as it is the most important block in the system. However, utilizing an efficient optimization approach for design of analog circuits has not been investigated yet. Moreover, the key specifications of the amplifier design such as noise sensitivity and operation bandwidth are not considered simultaneously in the previous works [7-9].In this work, a novel performance improvement approach is proposed that minimizes the computational effort while keeping the desired performance accuracy, simultaneously. This method uses a simulation-based multi-objective evolutionary algorithm to obtain the optimal circuit design points inside a limited practical deign space [10-12]. Focusing on a limited practical deign space results in reduced simulation time and computational burden whilst keeping a desired level of accuracy. The rest of the paper is organized as follows. Section 2 discusses the proposed amplifier design approach and the implemented circuit structure. Section 3 shows the simulation and evaluated results. Finally, a conclusion is given in Section 4.

2. Proposed Algorithm

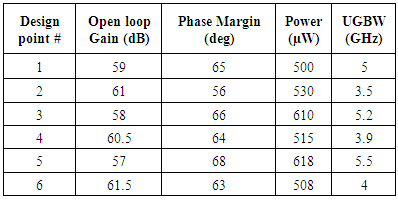

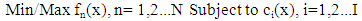

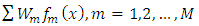

- The proposed optimization algorithm and the related MATLAB-HSPICE connection are shown in Fig. 1. The start point of this approach is to define the amplifier topology, process variation models, and the related performance functions [13-15]. The algorithm also generates a testbench netlist for the defined circuit topology and derives a set of design parameters under specified max/min conditions to change the amplifier performance. Then, the design space will be explored until obtaining the desired performance and finding out the best design point concerning a multi-objective function.

| Figure 1. Optimization process |

| (1) |

| (2) |

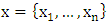

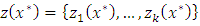

with n dimensions in the design space, X, (i.e., X introduces the whole design space), the amplifier optimization problem can be formulated in a way to find a vector, x*, that can minimize a set of K objective functions

with n dimensions in the design space, X, (i.e., X introduces the whole design space), the amplifier optimization problem can be formulated in a way to find a vector, x*, that can minimize a set of K objective functions  . The design space, X, is commonly constrained by a set of equality restrictions represented by

. The design space, X, is commonly constrained by a set of equality restrictions represented by  | (2) |

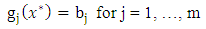

| Figure 2. Implemented amplifier architecture and corresponding chromosome |

3. Simulation Results

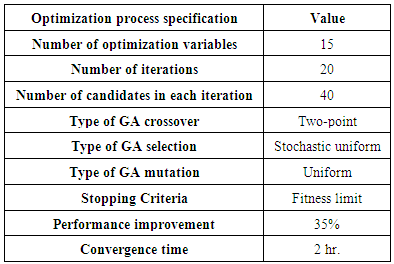

- Simulated in a 65nm CMOS technology with a power supply voltage of 1.0 V, the design performance has been verified at different process corner cases including slow, nominal, and fast models for both nMOS and pMOS devices as well as temperature variations spanning from –40°C to 85°C. Also, the actual MOS devices have been implemented to realize the switches controlled by different clock phases. To damp the oscillations caused by the bondwire parasitic inductors, the MOS decoupling capacitors are implemented. The optimization process is depicted in Fig. 2. Table 2 also lists an overal specification of the optimization process.

|

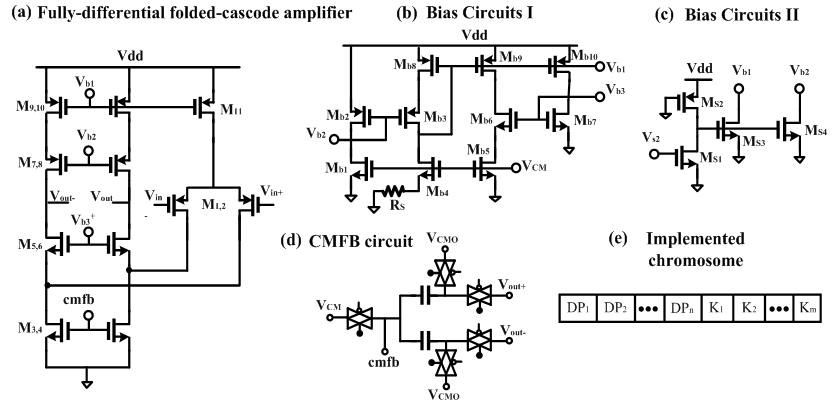

| Figure 3. Obtained pareto front points |

|

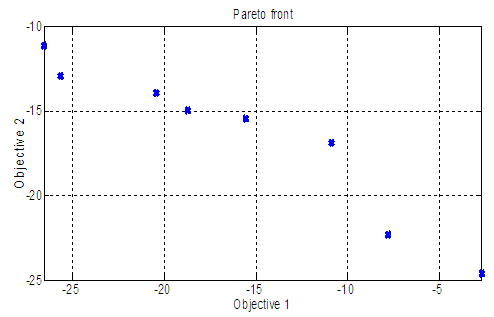

| Figure 4. Frequency response (a) before and (b) after optimization |

Abstract

Abstract Reference

Reference Full-Text PDF

Full-Text PDF Full-text HTML

Full-text HTML