-

Paper Information

- Next Paper

- Previous Paper

- Paper Submission

-

Journal Information

- About This Journal

- Editorial Board

- Current Issue

- Archive

- Author Guidelines

- Contact Us

Electrical and Electronic Engineering

p-ISSN: 2162-9455 e-ISSN: 2162-8459

2012; 2(2): 38-42

doi: 10.5923/j.eee.20120202.07

Optimization of a LNA Using Genetic Algorithm

Mojtaba Behzad Fallahpour 1, Kamran Delfan Hemmati 2, Ali Pourmohammad 3

1Young Researcher Club of Lahijan Islamic Azad University, Lahijan, Iran

2Sadjad Institute of Higher Education, Mashhad, Iran

3Electrical Engineering Department, Amirkabir University of Technology, Tehran, 15914, Iran

Correspondence to: Mojtaba Behzad Fallahpour , Young Researcher Club of Lahijan Islamic Azad University, Lahijan, Iran.

| Email: |  |

Copyright © 2012 Scientific & Academic Publishing. All Rights Reserved.

In this paper an accurate method is presented for determining of the device sizes in a RF circuit based on genetic algorithm (GA). HSPICE RF simulation is used for evaluating of the fitness of the circuit specifications per every iteration of the GA. Also an example for a LNA is presented for evaluating of non-dominated sorting genetic algorithm (NSGA-II) as a method of multi objective genetic algorithm optimization. Simulation results confirm efficiency of the GA for determining of the devices sizes and optimization in a RF circuit.

Keywords: Genetic Algorithm (GA), LNA, NSGA II

Article Outline

1. Introduction

- Even we are in the digital age and digital circuits directly benefit from advances in IC technologies, RF circuits do not as much. This issue is exacerbated by this fact that RF circuits often require external components - for example, inductors – where it is difficult bringing of them into the chip even in modern IC processes. In fact, computer aided analysis and synthesis tools for RF ICs are still in their infancy which it is forcing the designers to rely on experience, intuition, or inefficient simulation techniques to predict the performance. For example, nonlinearity, time variance, and noise in RF circuits usually require studying the spectrum of signals, but the standard ac analysis available in SPICE uses only linear, time invariant models[1]. Therefore, developing reliable automatic tools in RF IC design seems very attractive. One solution to this problem is employing Evolutionary Computing and in particular Genetic Algorithms (GA). Genetic Algorithm is a global search algorithm, which it models the process of the natural evolution in order to optimize the parameters of a problem. Genetic algorithm utilizes a non-gradient-based random search and is used in the optimization of complex systems[2]. In this paper, an example for a LNA which was described in reference[3] is presented in 0.18μm process for evaluation of non-dominated sorting genetic algorithm (NSGA-II) as a method of multi objective genetic algorithm optimization. Simulation results confirm efficiency of the GA for determining of devices sizes and optimization of a RF circuit. This paper is organized as follow: In Section II a LNA which was described in reference[3] is presented. A brief background of NSGA-II is given in section III. In section IV, Calculation of fitness function and in section V, simulation results are provided to verify the performance and capability of the proposed method. Finally performance of presented method in this work is compared with previous works.

2. LNA

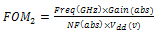

- Low noise amplifiers (LNA) are one of the key building blocks for RF receivers. They play a critical role for determining the overall system noise figure (NF) of the receiver[4]. The main function of an LNA is to provide sufficient gain to overcome the noise of subsequent stages (e.g. mixers) while adding as little noise as possible. For all kinds of receiver’s architecture, LNA is the first block to interface the weak RF signal coming from the antenna and duplexer. The noise performance and gain of LNA have a significant impact on the overall system noise performance[5]. In this work, a LNA which described in reference[3] (Fig. 1) is designed by using NSGA-II as a method of multi objective genetic algorithm optimization and HSPICE RF as evaluator tool. The reason we choose multi objective method for optimization is that RF circuits usually have several parameters. They are against together and designers need to trade off between these objectives such as gain, BW (band width), phase margin, power, noise figure (NF) and so on. The reason for choosing of NSGA-II among the other algorithms is low complexity and high efficiency of its algorithm for optimization. Also, we chose a LNA which is described in reference[3], because was designed as one of the best LNAs with the best parameters till 2010. The performance summary of chose LNA and comparison to other CMOS LNAs are shown in Table 1. Where Vdd is power supply, NF is noise figure, Ss are S parameters and FOMs are figure of merit. One figure of merit of the LNA is the ratio of the gain in dB to the noise figure in dB. Also FOM2 is[3]:

| (1) |

| Figure 1. Schematic and small signal equivalent of LNA[3] |

3. NSGA-II as an Optimization Algorithm

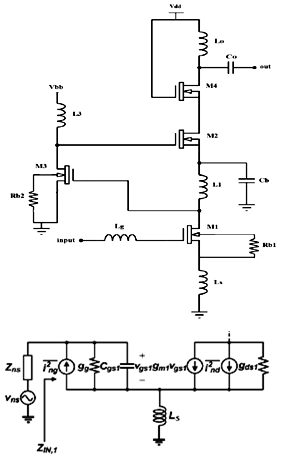

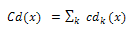

- Most of actual optimizing questions are naturally multi objective. It means that several objects must estimate at the same time. There are two views for solving multi objective optimizing questions. In the first method, we combine objects together, and then give weight to them to change the question to a single objective one. In this condition a certain weight will be given to each objective and objectives with higher priority will be assigned more weight to them. But the problem is that, in actual optimizing questions, objectives have no specific priority to each other. So it is not clear what weight should be allocated to each objective. Another method is using of ˝non-dominated˝. In this method, each objective is optimized separately, so that we obtain a bunch of non-dominated answers called ˝pareto optimal answers ˝. None of these answers have any priority to each other, according to all goal functions. So we can select each of them on the basis of our need. multi objective genetic algorithm uses such a technique to optimize multi objective problems .In many of optimizing questions , objectives are in opposition to each other .so the improvement in one may destroy the others . The problem causes the increasing numbers of ˝pareto front ˝after a few repeat. The result of this increasing is disorder in performance of program. To solve this problem, many algorithms have suggested in recent years. In ˝SPEA˝ algorithm, that presented by ˝Zitzler˝, the numbers of pareto front preserve in an external archive .there will use of a classification algorithm to reduce numbers of pareto front if the numbers of pareto front cross from distinct border. The classification is done in this way: the crowding distance between remained non-dominated numbers should be preserved. In fact, those numbers that their similar or close answers are available will be deleted from the cycle .Also ˝Deb˝ and his colleague introduced a method called ˝non-dominated sorting genetic algorithm˝ (NSGA2) .this method uses non-dominated ranking for ˝elitism˝ and implementing of ˝population distance˝ for preservation of answers crowding[12-13]. The operation of NSGA-II is illustrated in Figure 2 [14]. First, we form a random primal N sized population. By using usual operators of genetic algorithm another N members are made.

| Figure 2. Illustration of the operation of NSGA-II.[12] |

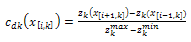

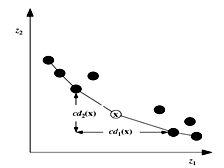

| (2) |

| (3) |

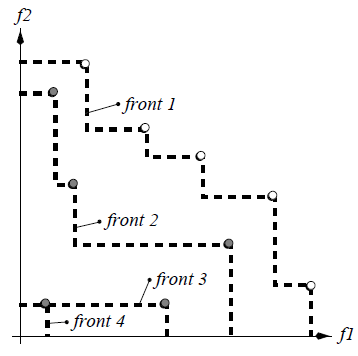

is a goal function and

is a goal function and  are maximum and minimum for this function (Figure 4)[15].

are maximum and minimum for this function (Figure 4)[15]. | Figure 3. Front of NSGA-II[13] |

| Figure 4. The calculate of crowding distance [15] |

4. Fitness Function Calculation

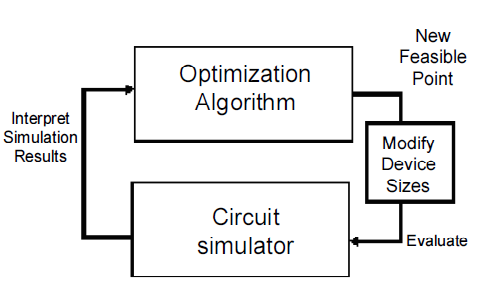

- First step of simulation of mentioned algorithm using MATLAB and HSPICE RF, the net list of each parameters vector is created and HSPICE RF is called. Then, the output file of HSPICE RF is used for object evaluation. In fact, a LNA using GA as a search algorithm and HSPICE RF tool as the fitness evaluator, is designed (Figure 5).

| Figure 5. Optimization Procedure[2] |

5. Simulation and Results

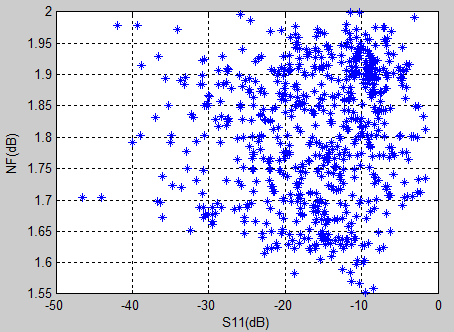

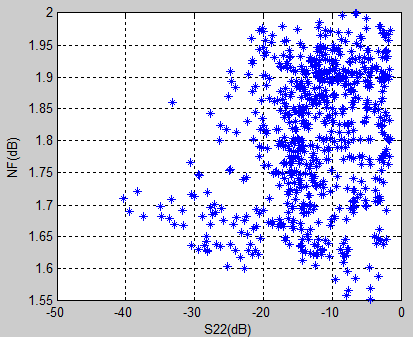

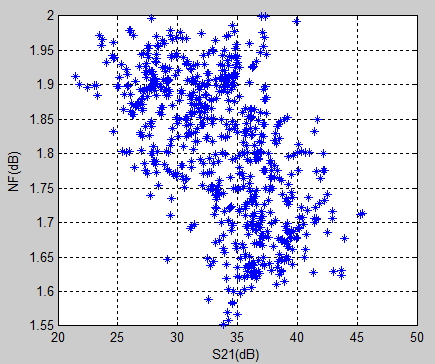

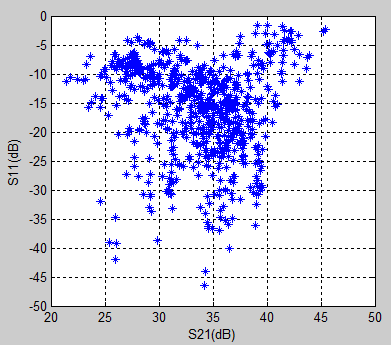

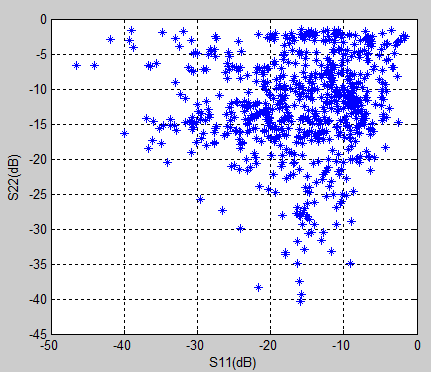

- Using GA program, the circuit size vector and the performance characteristics are shown in Table 2. Also Figures 6, 7, 8,9,10 show genetic algorithm process. Figures illustrate that executed algorithm is converged to the optimized point after 600 generations with initial population which is equal to 100. Follow execution of GA program, the performance characteristics were obtained which were better than the desired objects in reference[3]. The circuit size vector and the performance characteristics and optimized value are shown in Table 2.

| Figure 6. Multi objective optimization (NF vs. S11) |

| Figure 7. Multi objective optimization (NF vs. S22) |

| Figure 8. Multi objective optimization (NF vs. S21) |

| Figure 9. Multi objective optimization (S11 vs. S21) |

| Figure 10. Multi objective optimization (S22vs S11) |

|

|

6. Conclusions

- In this paper Genetic Algorithm and simulation based optimization were combined to produce an accurate tool for LNA designing. Also we show that multi objective algorithms like NSGA-II are some of the best methods for designing of this kind of RF circuits where they can be even used for designing of other characteristics as distortion behaviour and so on. The proposed method which it used for designing of this circuit is a general method and it is usable for any other types of RF circuits.

References

| [1] | B. Razavi, “RF Microelectronics”, Prentics-Hall, Upper Saddle River, 1997. |

| [2] | M. Taherzadeh, R. Lotfi, H. Zare and O. Shoaei, "Design optimization of analog integrated circuits using simulation-based genetic algorithm", Proc. IEEE International Symposium on signals and circuits, Vol. 1, pp. 73-76, July 2003. |

| [3] | E. Kargarn, H. Khosrowjerdi, K.Ghaffarzadegan and H. Nabovati, "A 5.7 GHz low noise figure ultra high gain CMOS LNA with inter stage technique", IEICE Electronics Express, Vol. 7, no.23,1686-1693. |

| [4] | G. Tulunay, S. Balkır, “A Compact Optimization Methodology For Single-Ended LNA”, IEEE, ISCAS, pp273-276, 2004. |

| [5] | D.Feng, B .Shi, “Comprehensive Analysis and Optimization of CMOS LNA Noise Performance”, IEEE. ASP.DAC.,pp . 1204-1207, 2005. |

| [6] | Y.S. Wang, L. H. Lu, "5.7 GHz low-power variable-gain LNA in 0.18 µm CMOS", Electron. Lett., vol. 41, pp. 66-68, 2005. |

| [7] | C.-Y. cha, S.-G. Lee, "A 5.2 GHz LNA in 0.35 µm CMOS utilizing inter-stage series response and optimizing the substrate resistance”, IEEE j. Solid-Stage Circuits, vol. 38, no.4, pp.. 669-672, April 2003. |

| [8] | C.-H. Liao, H. R.Chuang, “A 5.7GHz 0.18µm CMOS gain-controlled differential LNA with current reuse for WLAN receiver”, IEEE Microw.Wireless Compon. Lett., vol.13, no.12, pp.526-528, Dec. 2003. |

| [9] | J.S. Walling, S .Shekhar, and D.J.Allstot, “A gm-Boosted Current-Reuse LNA in 0.18 µm CMOS”, IEEE radio FREQ. Inter.Circuits Symp.,pp . 613-616 ,3-5 June 2007. |

| [10] | E.H. Westerwick, "A 5 Ghz band CMOS low noise amplifer with a 2.5 dB noise figure Low", Proc. Ieee Symp. VLSI Tech. Syst.Appl., pp. 224-227, 2001. |

| [11] | H.-W. chiu, S.-S. Lu,and Y.-S.lin, "A 2.17-dB NF 5-GHz- band mono-lithic CMOSLNA with 10-mW dc power consumption", IEEE Trans.MIcrow.Theory Tech., vol.53, no. 3, pp. 813-824, March 2005. |

| [12] | El-Sayed M. El-Alfy, "Flow-Based Path Selection for Internet Traffic Engineering with NSGA-II", IEEE 17th Internation conferece on Telecommunications,, pp. 621 – 627, 2009. |

| [13] | E. Zitzler, “Evolutionary Algorithms for Multiobjective Optimization: Methods and Applications”, PhD thesis, Swiss Federal Institute of Technology, Zurich, Switzerland, 1999. |

| [14] | K. Deb, A. Pratap et al, S.Agarwal, T.Meyarivan, “A fast and elitist multi-objective genetic Algorithm: NSGA-II”, IEEE Trans. On Evolutionary Computation, Vol. 6, no.2, pp.182-197, 2002. |

| [15] | S.Babayan Mashhadi, "Optimizing the Design of Low- voltage and Low- Power Analog Integrated Circuits using Multi-objective Genetic algorithms", A dissertation submitted in partial fulfillment of the requirements For the degree of Master of Science in Electrical Engineering In the graduate division Of the Ferdowsi University of Mashhad. |

Abstract

Abstract Reference

Reference Full-Text PDF

Full-Text PDF Full-Text HTML

Full-Text HTML